## X-Wall FX-128; X-Wall FX-192; X-Wall FX-256 X-Wall FX-128C; X-Wall FX-192C; X-Wall FX-256C USB2.0 to Serial ATA Real-time Cryptographic Processor Specification Rev. 1.5

## **Revision History**

| Rev No. | Description                                       | Author     | Rev. Date  |

|---------|---------------------------------------------------|------------|------------|

| 1.0     | Initial release.                                  | C. Y. Chiu | 06/03/2008 |

|         |                                                   | R. Wann    |            |

|         |                                                   | B. Huang   |            |

| 1.1     | General editing.                                  | C. Y. Chiu | 07/04/2008 |

|         |                                                   | R. Wann    |            |

|         |                                                   | B. Huang   |            |

| 1.2     | Updating Packaging Information                    | R. Wann    | 07/15/2008 |

| 1.2.1   | Revise page 4 - Authentication                    | R. Wann    | 07/18/2008 |

| 1.3     | Adding Power Trace Layout on page 16              | C. Y. Chiu | 12/262008  |

|         | Adding PCB Parameters for Differential Signals on | B. Huang   |            |

|         | page 17                                           | _          |            |

| 1.4     | Add electrical characteristics over power         | C. Y. Chiu | 04/08/2009 |

|         | consumption on page 19;                           | R. Wann    |            |

|         | Update operating temperature on page 19;          |            |            |

|         | General editing                                   |            |            |

| 1.5     | Update patent, layout, and contact information    | R. Wann    | 07/29/2010 |

|         | Intentionally left blank                          |            |            |

#### Asia

Enova Technology Corporation 1<sup>st</sup> Floor, #11, Research & Development 2<sup>nd</sup> Rd. Science-based Industrial Park, Hsin-Chu City Taiwan 30076, Republic of China Tel. +886 3 577 2767 Fax +886 3 577 2770 <u>http://www.enovatech.net</u> info@enovatech.net

#### North America

Enova Technology 1918 Junction Avenue San Jose, California 95131, USA Tel. +1 408.679.2949

http://www.enovatech.com info@enovatech.com

## **Table of Content**

| Background                                                          | 3  |

|---------------------------------------------------------------------|----|

| Functional Blocks                                                   | 3  |

| Authentication                                                      | 4  |

| X-Wall FX 2-wire Serial Interface Basic                             | 5  |

| Solutions Using the X-Wall FX                                       | 6  |

| One Time Setup Making Truly Portable                                | 7  |

| Support Over Than 2TB                                               | 7  |

| Professional and Premium Version                                    | 8  |

| Administrator Password Controls Users Access                        | 8  |

| Reliable Disk Operation Using Enova Real-time Encryption Technology | 8  |

| Features                                                            | 9  |

| System Requirement                                                  | 9  |

| X-Wall FX Pin Definitions                                           | 10 |

| Pin Assignment                                                      | 10 |

| PCB Layout Guidelines                                               |    |

| Typical Application Schematics                                      | 14 |

| Typical Bill of Materials (BOM)                                     | 14 |

| Component Placement                                                 | 16 |

| PCB Trace Routing                                                   | 16 |

| SATA Signal Layout                                                  | 16 |

| USB Signal Layout                                                   | 16 |

| Power Trace Layout                                                  | 16 |

| PCB Parameters of Differential Signals                              | 17 |

| Electrical Characteristics                                          |    |

| Absolute Maximum Ratings                                            | 18 |

| DC Characteristics                                                  | 18 |

| X-Wall FX Configuration Management                                  | 19 |

| Hardware Packaging                                                  | 19 |

| Features                                                            | 19 |

| Firmware Release                                                    | 19 |

| Hardware version control, outline, and dimension                    | 19 |

## Background

Enova Technology proudly introduces *X-Wall FX*, the USB/SATA real-time cryptographic bridge processor that is capable of conducting real-time full disk encryption over the connected SATA disk drives<sup>1</sup>. The **patents protected<sup>2</sup> FX** is the 8<sup>th</sup> generation of the *X-Wall* real-time full disk encryption technology. It equips with tightly integrated USB 2.0 and SATA interface controller that allows the connection of SATA disk drives to a host USB 2.0 interface controller, making it a perfect fit for modern USB interfaced external storage enclosure as well as other USB and SATA related security storage solutions. Additionally, the *FX* offers NIST and CSE certified real-time hardware AES<sup>3</sup> security up to 256-bit encryption strength to safeguard the entire content of the SATA disk drive. The operations of encryption and decryption are totally transparent for reliable disk drive operations. Your privacy and confidentiality are always kept safely from prying eyes with the *FX* enabled.

Most importantly, the *X*-*Wall FX* is authenticated by a password entry from your personal computer keyboard as a pre-boot condition. At initialization, you get to select your pass phrase and the *FX* writes both <u>encrypted</u> pass phrase and AES secret key to the connected SATA disk drive. The loading of all authentication software is completely transparent to all users to ensure that there are no user interruptions. For user login, the password entry will be compared internally inside the *FX* to avoid attacks attempted over the host computer.

The *X-Wall FX* offers absolutely no performance degradation<sup>4</sup> during entire cryptographic operations. In lots of applications, the *X-Wall FX* enhances the speed and performance of your disk read/write. Thanks to its advanced real-time pipeline engine design, the *X-Wall FX* with its hardware AES engine enabled, surpasses all other generic peer controllers.

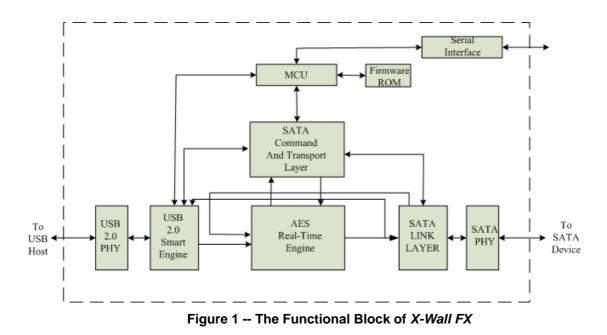

#### **Functional Blocks**

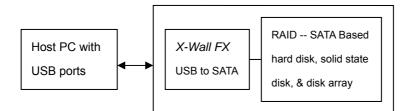

As shown in Figure 1, the *X*-*Wall FX* offers a standard USB 2.0 device controller to the host computer and a standard SATA host controller to allow the controls over a SATA based disk drive including solid state disk (SSD). Without the enabling of the powerful real-time AES cryptographic capability, the *FX* simply serves as a standard USB 2.0 to SATA disk controller.

SATA 2.0 drives can be operated on the *X-Wall FX* without performance degradation.

US patents 7,136,995; 7,386,734; and Application 11/282,175. Taiwan & PR China patent

<sup>625110.</sup>

<sup>&</sup>lt;sup>3</sup> NIST and CSE certification is essential as the authenticity and quality of AES implementation are proven. Enova Technology's hardware AES ECB and CBC crypto engine certifications can be viewed at <u>www.enovatech.com</u>.

The performance test report can be viewed at our website.

Engineering design is simple and straight forward with the *X-Wall FX* as both standard USB 2.0 PHY and Smart Engine are built in. More, the SATA interface controller PHY, Link, and Transport layers are tightly integrated with all the USB functional blocks to form the complete circuit. Real-time hardware AES cryptographic engine is at the heart of the entire circuit, offering real-time no performance loss performance to both USB host and SATA device controller (the SATA disk drive). An embedded micro controller manages Power-On-Self-Test (POST) and several cryptographic operations/functions including Built-In-Self-Test (BIST), 2-wire serial communication protocol, and password authentication.

#### **Authentication**

Authentication is provided through either Host Password or built-in 2-Wire Serial Protocol. <u>You</u> <u>can not use both as they are mutually exclusive</u>. Either the Host Password or the 2-Wire Serial Protocol authentication method enables the built-in real-time hardware AES capabilities. There are certain constraints in using those however.

For Host Password, the limitation lies over the Operating System the *X-Wall FX* would be able to support. Please reference to **System Requirement** at page 9 for details. Having said, without using the Host Password, the *X-Wall FX* simply acts as a standard USB/SATA bridge controller without providing the real-time hardware AES capabilities.

For Device Side Authentication using 2-wire Serial Protocol, extra micro controller is needed to communicate properly during user authentication. The design can be versatile including those popular Finger Print, Smart Card, Key Pad, Key Fob, or any combination. If none of the Host Password and

2-wire Serial Protocol is been used, the *X-Wall FX* simply acts as a standard USB/SATA bridge controller without providing the real-time hardware AES capabilities.

Host Password – Password based authentication software are supported to allow fast to market.

Password management can be customized to meet with your specific design taste and requirement.

The Advanced vs. Basic version X-Wall FX offers unique proposition in security and password

management, which are done through software and continuous upgrade. <u>Enova Technology also</u>

offers advanced SDK<sup>5</sup> to help facilitate various designs, including remote access and

management.

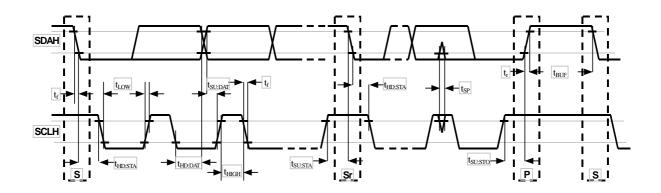

**2-Wire Serial Protocol** – Just like all prior generation *X-Wall* family chips, the *X-Wall FX* equips with 2-wire serial protocol for key loading that enables the real-time hardware AES cryptographic engine. The 2-wire serial protocol and password are mutually exclusive, meaning authentication can only choose either one, not both. Below diagram shows the 2-wire serial protocol timing that designers may follow through.

#### X-Wall FX 2-wire Serial Interface Basic

The bus interface has two bus wires. The first one, namely SDAH, is used for transmitting and receiving serial bit data. The second one, namely SCLH, is used for transmitting (master mode) and receiving (slave mode) clock pulses. By combining those two signals the START, repeated START, and STOP conditions are created, which are then used for constructing entire bus protocol. Listed below are signal-timing specification of SDAH and SCLH.

| PARAMETER                                            | SYMBOL              | MIN. | MAX. | UNIT |

|------------------------------------------------------|---------------------|------|------|------|

| SCL clock frequency                                  | f <sub>sc∟</sub>    | 0    | 400  | kHz  |

| Hold time (repeated) START condition (S). After this | t <sub>HD:STA</sub> | 0.6  | -    | μs   |

<sup>&</sup>lt;sup>5</sup> The SDK is available for licensing. This powerful SDK allows the designers to control specific registers and hard disk sectors. Consult with Enova Engineering at <u>info@enovatech.com</u> for licensing details.

|                                                           |                     |                      | T   | T  |

|-----------------------------------------------------------|---------------------|----------------------|-----|----|

| period the first clock pulse is generated.                |                     | <u> </u>             |     |    |

| LOW period of the SCL clock                               | t <sub>LOW</sub>    | 1.3                  | -   | μs |

| HIGH period of the SCL clock                              | t <sub>HIGH</sub>   | 0.6                  | -   | μs |

| Set-up time for a repeated START condition (Sr)           | t <sub>su:sta</sub> | 0.6                  | -   | μs |

| Data hold time                                            | t <sub>HD:DAT</sub> | 0                    | 0.9 | μs |

| Data set-up time                                          | t <sub>su:dat</sub> | 100                  | -   | ns |

| Rise time for both SDA and SCL signals                    | tr                  | 20+0.1C <sub>b</sub> | 300 | ns |

| Fall time for both SDA and SCL signals                    | t <sub>f</sub>      | 20+0.1C <sub>b</sub> | 300 | ns |

| Setup time for STOP condition (P).                        | t <sub>su:sто</sub> | 0.6                  | -   | μs |

| Bus free time between a STOP and a START                  | t <sub>BUF</sub>    | 1.3                  | -   | μs |

| condition.                                                |                     |                      |     |    |

| Pulse width of spikes, which must be suppressed by        | t <sub>SP</sub>     | 0                    | 50  | ns |

| the input filter.                                         |                     |                      |     |    |

| C <sub>b</sub> : total capacitance of one bus line if pf. |                     |                      |     |    |

## Solutions Using the X-Wall FX

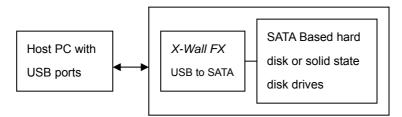

**USB Portable Drive** – The *X-Wall FX* real-time cryptographic processor along with its built-in password authentication software serve as a complete single chip solution for all USB 2.0 based external storage including SATA based disk drive and solid state disk. As shown in *Figure 2, A real-time hardware AES secured USB portable disk*, the system configuration is the same as a regular USB 2.0 external storage enclosure except that *FX* offers unprecedented NIST and CSE certified hardware real-time AES encryption capability for both ECB (Electronic Code Book) and CBC (Cipher Block Chaining) mode of operations.

Figure 2 -- A real-time hardware AES secured USB portable disk

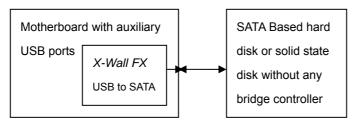

**Secure Motherboard** – The *FX* can be mounted over a standard motherboard auxiliary USB port, making the USB port secured for an external SATA disk drive connection. The external SATA disk drive can be as easy as a SATA disk with fixture (without any type of bridge controller) only. Please reference below **Figure 3**, **A real-time hardware AES secured SATA and Solid State Disk**, of which the connected SATA disk or Solid State Drive is secure without any extra bridge controller as the main functions are been performed over the *X-Wall FX*, which is directly mounted over the mainboard.

Figure 3 -- A real-time hardware AES secured SATA and Solid State Disk

Secure SATA Disk Array Over Than 2TB – The *X-Wall FX* real-time cryptographic processor along with its built-in password authentication software serve as a complete single chip solution for all USB 2.0 based external SATA based disk array. The entire SATA disk array is secured using single *X-Wall FX* controller, as long as the disk array has equipped with a standard SATA connection to the host. As shown in *Figure 4, A real-time hardware AES secured USB disk array*, the system configuration is the same as a regular USB 2.0 external storage enclosure except that *FX* offers unprecedented *NIST* and *CSE* certified hardware real-time AES encryption capability for both ECB (Electronic Code Book) and CBC (Cipher Block Chaining) mode of operations.

Figure 4 -- A real-time hardware AES secured SATA Disk Array Over Than 2TB

## One Time Setup Making Truly Portable

The initialization procedure takes only one time and does not require you to conduct another setup procedure when you move your *X-Wall FX* secured USB portable drive to another host computer, making the portable drive truly portable and secure wherever you travel. To access the secure portable USB disk while you travel, simply double-click the setup files found over the secure portable disk drive then enter your password.

## Support Over Than 2TB

The *X-Wall FX* supports over than 2 Tera Bytes of the USB external storage, which means you get to connect a SATA based RAID disk array over than 2TB but are still able to enjoy the hardware real-time AES security over the entire disk array using only one single *X-Wall FX* chipset. Please be advised, however, that the SATA based RAID disk array will need to be equipped with a SATA input

interface for proper connection to the SATA interface controller of the *FX*. The password based authentication software will still function correctly under this type of configuration. The *FX* solution offers yet another unprecedented disk volume support.

## Professional and Premium Version

There will be a family of six (6) *X-Wall FX* chips with different bundled authentication software. The cryptographic strength of all six is different and is therefore listed below:

| Ordering Code  | AES Mode of           | Real-time     | Authentication   |

|----------------|-----------------------|---------------|------------------|

| (SKU)          | Operation             | Cryptographic | Software Bundled |

|                |                       | Strength      |                  |

| X-Wall FX-128  | Electronic Code Book  | 128-bit       | Premium          |

| X-Wall FX-192  | Electronic Code Book  | 192-bit       | Professional     |

| X-Wall FX-256  | Electronic Code Book  | 256-bit       | Professional     |

| X-Wall FX-128C | Cipher Block Chaining | 128-bit       | Professional     |

| X-Wall FX-192C | Cipher Block Chaining | 192-bit       | Professional     |

| X-Wall FX-256C | Cipher Block Chaining | 256-bit       | Professional     |

## Administrator Password Controls Users Access

The Advanced version of the *X-Wall FX* equips with both Administrator and User Password. The Administrator gets to manage the user's password in terms of issuance, rights revocation, alternation, and recovery. There is an interlocking mechanism on the number of either the user or administrator's failed attempts. Once the user is locked after multiple failed attempts, only the Administrator can unlock the *X-Wall* secure SATA disk drives. The Basic version offers only User Password and similar interlocking mechanism. Attempts to probe into the passwords are futile as both are encrypted using the hardware AES cryptographic engine that *X-Wall FX* equips.

## Reliable Disk Operation Using Enova Real-time Encryption Technology

Hardware encryption is always better than software in terms of security and reliability. For one thing, hardware does not crash your data like software often does. The crash over using a software encryption product usually causes irreparable harm. By using an Enova *X-Wall FX* solution, you get to perform all regular software backup tasks without complications. Additionally, the software encryption product needs a clear text key for cryptographic operations and such key resides in the system memory. A memory dump can easily recover such key value thus defeat the whole purpose of being

Page 8 of 20

secure. The *FX* uses the same clear text key but only within its internal key registers which are not readable through any interfaces. When the power is gone, the entire content of the key registers are gone, thus can successfully defeat the exploitation of the keys through any type of memory dump techniques. More, the *FX* performs all cryptographic functions within the chip level to ensure the highest attainable security level.

## **Features**

- 1. Complies with SATA 2.6 Specification

- 2. Complies with USB2.0 Specification

- 3. Tightly integrated USB2.0 and SATA interface single chip controller

- 4. Supports hardware real-time AES cryptographic capability to entire SATA disk drive including SSD (Solid State Disk) up to 256-bit in both ECB and CBC mode

- 5. Supports standard USB/SATA bridge function without AES cryptographic function

- 6. Supports LBA 48-bit addressing

- 7. Supports over than 2TB per X-Wall FX

- 8. Low profile 64-pin QFP package

## System Requirement

- 1. USB2.0 High Speed at 480Mbit/sec and Backward Compatible;

- 2. All SATA Disk Drives including SATA Compliant SSD;

- Windows Vista 32/64-bit, XP 32-64-bit, Windows 2000 32-bit With Real-time Cryptographic AES Strength Through Either Host Password or 2-Wire Serial Protocol authentication (Device Password);

- 4. Host Password and 2-Wire Serial Protocol Are Mutually Exclusive;

- 5. All Operating Systems For A Standard USB/SATA Bridge Controller (Without Real-time Cryptographic AES Capabilities);

- 6. All Operating Systems Using Only 2-Wire Serial Protocol For Real-time Cryptographic AES Cryptographic Capabilities;

## X-Wall FX Pin Definitions

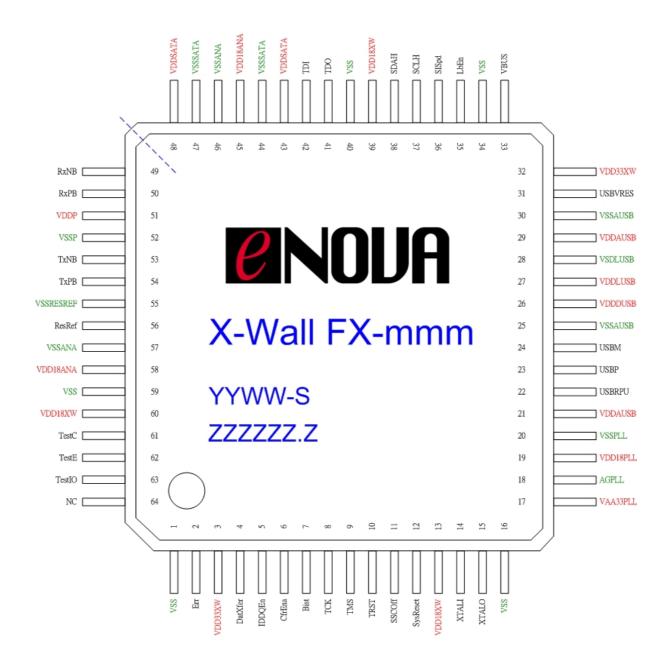

#### Pin Assignment

All X-Wall FX family ASIC shares the same pin assignment and pin definition. Upgrading from a lower strength, for instance, from an X-Wall FX-128 to an X-Wall FX-256 is as easy as replacing the chip and the actual Secret Key.

Copyright 2010 © Enova Technology Corporation. All rights reserved. X-Wall FX Specification Rev1.5 July292010.doc

|             | SATA PHY INTERFACE |     |                |                                                                     |  |

|-------------|--------------------|-----|----------------|---------------------------------------------------------------------|--|

| NAME        | PIN*               | DIR | TYPE           | DESCRIPTION                                                         |  |

| pinRxPB     | 50                 |     |                | Receiving differential input signals for SATA channel.              |  |

| pinRxNB     | 49                 | •   |                |                                                                     |  |

| pinTxPB     | 54                 | 0   |                | Differential serial output transmit signal for SATA channel.        |  |

| pinTxNB     | 53                 | -   |                |                                                                     |  |

| pinResRef   | 56                 | I/O |                | Reference register, terminated to pin VSSREFREF through             |  |

|             |                    |     |                | 2.7K±1% ohms.                                                       |  |

| Total       | 5                  |     |                |                                                                     |  |

|             |                    |     |                | USB PHY INTERFACE                                                   |  |

| NAME        | PIN                | DIR | TYPE           | DESCRIPTION                                                         |  |

| pinUSBP     | 23                 | I/O |                | USB data pin data+                                                  |  |

| pinUSBM     | 24                 | 1/0 |                | USB data pin data-                                                  |  |

| pinUSBRPU   | 22                 | 1/0 |                | Connected to an external 1.5K Ohm pull-up resister.                 |  |

| pinUSBVRES  | 31                 | 1/0 |                | Connected to an external 6.195K Ohm resister for band-gap           |  |

| p           | •.                 |     |                | reference circuit.                                                  |  |

| pinVBUS     | 33                 |     |                | Connect to VCC at USB connector to detect if USB Bus is             |  |

|             |                    |     |                | connected.                                                          |  |

| Total       | 5                  |     |                |                                                                     |  |

|             |                    |     | CLO            | OCK AND PLL CONTROL PINS                                            |  |

| NAME        | PIN                | DIR | TYPE           | DESCRIPTION                                                         |  |

| pinXTALI    | 14                 |     |                | Crystal/reference clock input.                                      |  |

| printin     |                    |     |                |                                                                     |  |

| pinXTALO    | 15                 | 0   |                | Crystal/reference clock output                                      |  |

| p           |                    | -   |                |                                                                     |  |

| Total       | 2                  |     |                |                                                                     |  |

|             |                    |     |                | FEATURE SETTING PINS                                                |  |

| NAME        | PIN                | DIR | TYPE           | DESCRIPTION                                                         |  |

| pinCfrEna   | 6                  | 1   |                | Cryptographic engine enabled.                                       |  |

| pinSSCOff   | 11                 | i   |                | Turn off (HIGH) SSC mode for transmitting.                          |  |

| Total       | 2                  |     |                |                                                                     |  |

|             |                    |     | CON            | TROL AND INDICATE SIGNALS                                           |  |

| NAME        | PIN                | DIR | TYPE           | DESCRIPTION                                                         |  |

| pinSysReset | 12                 |     |                | Hardware master reset.                                              |  |

| pinSysteset | 2                  | 0   |                | If BIST is set to logic one, a HIGH at this pin indicates that the  |  |

|             | -                  | Ŭ   |                | build-in self-test in PHY has failed. If cryptographic mode is      |  |

|             |                    |     |                | selected, an active HIGH at this pin indicates that errors found in |  |

|             |                    |     |                | reading Key data, Key token not attached, or power-up self-test     |  |

|             |                    |     |                | (POST) for Cipher Engine has failed.                                |  |

| pinDatXfer  | 4                  | 0   |                | Active LOW at this pin indicates that X-Wall FX has detected data   |  |

| ,           |                    | -   |                | transfer activities on its channels.                                |  |

| Total       | 3                  |     |                |                                                                     |  |

|             | -                  |     | 2              | 2-WIRE SERIAL INTERFACE                                             |  |

| NAME        | PIN                | DIR | TYPE           | DESCRIPTION                                                         |  |

| pinSDAH     | 38                 | I/O | 8mA            | 2-Wire Serial Data.                                                 |  |

| pinSCLH     | 37                 | 1/0 | 8mA            | 2-Wire Serial Clock.                                                |  |

| pinSISpd    | 36                 |     |                | Select 2-wire serial interface speed. Standard speed = 1, fast      |  |

| 1 -1        | _                  |     |                | speed = 0.                                                          |  |

| Total       | 3                  |     |                |                                                                     |  |

|             |                    |     |                | JTAG TEST PINS                                                      |  |

| NAME        | PIN                | DIR | TYPE           | DESCRIPTION                                                         |  |

|             |                    |     | · · · <b>—</b> |                                                                     |  |

| pinTCK                                                               | 8                              | I   |      | Test clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------|--------------------------------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| pinTDI                                                               | 42                             | İ   |      | Test data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| pinTDO                                                               | 41                             | 0   |      | Test data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| pinTMS                                                               | 9                              | Ι   |      | Test mode select.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| pinTRST                                                              | 10                             | Ι   |      | Test reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Total                                                                | 5                              |     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                      |                                |     |      | DEBUG INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| NAME                                                                 | PIN                            | DIR | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| pinIDDQEn<br>pinBist<br>pinLbEn<br>pinTestC<br>pinTestE<br>pinTestIO | 5<br>7<br>35<br>61<br>62<br>63 |     |      | When asserted high, puts sataPhy into iDDQ test mode, whereby<br>all PLLs are disabled. This input is used for leakage current<br>testing. The power on reset signal (pOR) must be asserted high<br>prior to taking an iDDQ measurement. When negated low, this<br>signal allows the PLLs to resume normal operation.Turn on (HIGH) build-in-self-test (BIST) mode of PHY.PHY loop back mode enable under functional test (testIO = 0,<br>testC = 1, and testE = 1).Select test modes for scan tests and functional tests. Under scan<br>modes, PLL is powered down and its REF clock is multiplexed to<br>the PLLOUT clock to facilitate scan testing.testIOtestC00010101101001011001101010101010203040404040404040404040404040404040404040404040404040440 |

|                                                                      |                                |     |      | 1 1 0 SATA PHY transmit HFTP (D10.2)<br>1 1 1 SATA PHY transmit LBP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Total                                                                | 6                              |     |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                      |                                |     |      | POWER GROUND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| NAME                                                                 | PIN                            | DIR | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| pinVDD18ANA                                                          | 45<br>58                       |     |      | Analog 1.8V power for SATA PHY core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| pinVSSANA                                                            | 46<br>57                       |     |      | Analog ground of VDD18ANA. At least 2 VDD18ANA/VSSANA<br>pairs should be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| pinVDDSATA                                                           | 43<br>48                       |     |      | Digital 1.8V supply not to be shared with global digital supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| pinVSSSATA                                                           | 44<br>47                       |     |      | Digital ground of VDDSATA. Not to be shared with global digital ground. At least 3 VDDSATA/VSSSATA pairs should be used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| pinVSSRESREF                                                         | 55                             |     |      | Analog ground return for the external resistor reference. Should be as close to pinResRef as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| pinVDDP                                                              | 51                             |     |      | At least one for each Tx/Rx pair. And at least one un-bonded for each Tx/Rx pair for extra ESD protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| pinVSSP                                                              | 52                             |     |      | At least one for each Tx/Rx pair. And at least one un-bonded for each Tx/Rx pair for extra ESD protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PRCUT1P                                                              |                                |     |      | Used for DC isolation between supply domains (with different DC voltage) in IO ring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| pinVDD33XW                                                           | 3<br>32                        |     |      | Digital 3.3V supply of <i>X-Wall FX</i> I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| pinVDD18XW                                                           | 13<br>39<br>60                 |     |      | Digital 1.8V supply of <i>X-Wall FX</i> core.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| pinVSSXW    | 1  |        | Digital ground of X-Wall FX I/O and core. |

|-------------|----|--------|-------------------------------------------|

|             | 16 |        |                                           |

|             | 34 |        |                                           |

|             | 40 |        |                                           |

|             | 59 |        |                                           |

| pinVDD18PLL | 19 |        | Digital 1.8V core power supply for PLL.   |

| pinVSSPLL   | 20 |        | Digital ground of pinVDD18PLL.            |

| pinVAA33PLL | 17 |        | Analog 3.3V supply for PLL.               |

| pinAGPLL    | 18 | PVSS1A | Analog ground of pinVAA33PLL.             |

| pinVDDAUSB  | 21 |        | 3.3V analog power for USB macro.          |

|             | 29 |        |                                           |

| pinVSSAUSB  | 25 |        | Analog ground for USB macro.              |

|             | 30 |        |                                           |

| pinVDDDUSB  | 26 |        | 3.3V digital power for USB macro.         |

| pinVDDLUSB  | 27 |        | 1.8V digital power for USB macro.         |

| pinVSDLUSB  | 28 |        | Digital ground for USB macro.             |

| Total       | 32 |        |                                           |

## **PCB Layout Guidelines**

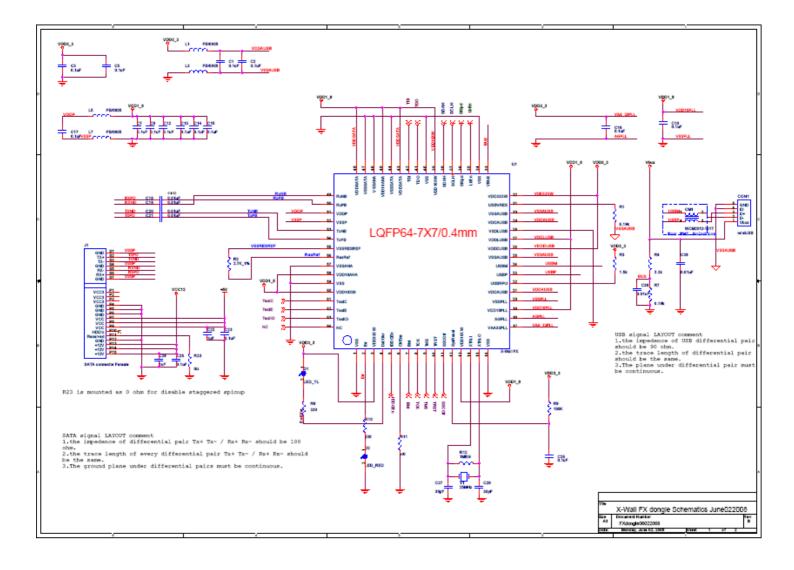

#### **Typical Application Schematics**

In a typical USB/SATA external storage enclosure application, the *X-Wall FX* is the single controller on board that controls both USB host and SATA device (the SATA disk drive). The typical password authentication does not require connection over the 2-wire serial bus but LED indicators may be included. For the detailed circuit layout files and Bill of Materials, please visit our website to download the latest revision. For special feature implementation such as customized SDK and some software source codes and related features, make a request with Enova Engineering at info@enovatech.com.

#### Typical Bill of Materials (BOM)

| ltem | Quantity | Reference | Part                   |

|------|----------|-----------|------------------------|

| 1    | 1        | CM1       | WCM2012-121T or 0 ohm* |

Copyright 2010 © Enova Technology Corporation. All rights reserved. X-Wall FX Specification Rev1.5 July292010.doc

| 2  | 2  | CON2,CON1                   | Mini-USB                     |

|----|----|-----------------------------|------------------------------|

| 3  | 19 | C1,C2,C3,C5,C7,C8,C10,      | 0.1uF                        |

|    |    | C12,C13,C14,C15,C16,        |                              |

|    |    | C17,C23,C25,C26,C33,C36,C37 |                              |

| 4  | 6  | C18,C19,C20,C21,C38,C39     | 0.01uF/0402                  |

| 5  | 2  | C22,C24                     | 1uF                          |

| 6  | 2  | C27,C28                     | 30pF                         |

| 7  | 5  | C29,C31,C32,C34,C35         | 10uF/16V TANT B              |

| 8  | 1  | D1                          | LED_YL/0603                  |

| 9  | 1  | D2                          | LED_RED/0603                 |

| 10 | 1  | J1                          | SATA connector Female DIP RA |

| 11 | 1  | J2                          | DC JACK-3/1.3mm              |

| 12 | 4  | L1,L3,L5,L7                 | FB/0805                      |

| 13 | 2  | R7,R1                       | 6.19k                        |

| 14 | 1  | R2                          | 2.7K_1%                      |

| 15 | 3  | R3,R16,R17                  | 1.5K                         |

| 16 | 1  | R4                          | 3.3k                         |

| 17 | 2  | R10,R8                      | 330                          |

| 18 | 1  | R9                          | 100K                         |

| 19 | 5  | R11,R13,R14,R18,R20,R22     | x/0                          |

| 20 | 1  | R12                         | 1MEG                         |

| 21 | 1  | R15                         | 10K                          |

| 22 | 2  | R21,R19                     | 33                           |

| 23 | 1  | R23                         | 0                            |

| 24 | 1  | U1                          | X-Wall FX                    |

| 25 | 1  | U2                          | AIC1117-33/SOT223            |

| 26 | 1  | U3                          | AIC1117-18/SOT223            |

| 27 | 1  | U4                          | AT24C02B 8P/SOIC             |

| 28 | 1  | Y1                          | 25MHz DIP                    |

|    |    |                             |                              |

\* Common choke is reserved for EMI solution .Two 0 ohm resistors can be mounted between pin1&pin2 and pin3&pin4 for USB signal connection if there isn't any EMI concern.

Copyright 2010 © Enova Technology Corporation. All rights reserved. X-Wall FX Specification Rev1.5 July292010.doc

#### **Component Placement**

- For each power pin, add one bypass capacitor, which should be placed closely to the power pin.

- The DC blocking capacitors on SATA signal traces (C18, C19, C20, and C21) should be placed closely to X-Wall FX.

- R1, R2, and R3 should be placed closely to X-Wall FX.

- The Crystal circuits should be placed closely to X-Wall FX.

#### PCB Trace Routing

The *X*-*Wall FX* SATA signals routing can become really tricky thus deserves careful attention. The following bullets serve as a general guideline when the signal routing is attempted. Noted, however, this guideline does not cover the entire horizon of a complete design other than dealing with *X*-*Wall MX* specifically.

#### SATA Signal Layout

- To route the ResRef and VSSRESREF signals, <u>DO NOT</u> connect these signals to the ground and no other signals traces are routed near by these traces. Use 20mil trace width to route these traces and keep them as short as possible.

- The SATA TX signal pairs and SATA RX signal pairs <u>MUST HAVE</u> matching trace length. The difference of two line traces in either TX signal pairs or RX signal pairs should be restricted to below 150 mils.

- No other signals should be routed near by these SATA traces on <u>ANY</u> layers. There should be no more than one via on these traces; and there should be no stub on these traces. Recommend to use DIP type SATA connector to avoid using more than one via. Keep these traces as short as possible. A solid ground plane should be placed directly underneath these traces to have better signal quality.

- The SATA TX signal pairs and SATA RX signal pairs <u>MUST HAVE</u> 100Ω differential impedance. To achieve aforementioned impedance value, Please refer to the paragraph of "PCB Parameters of Differential Signals."

- Do not route SATA traces underneath the crystal circuits or any other chips that employ high clocking.

#### **USB Signal Layout**

All SATA layout guidelines mentioned above must be followed precisely to guarantee the signal quality. When the USB differential signals are routed, please further include the followings:

- The impedance of the USB differential pair should be 90 ohms. Please refer to the paragraph "PCB Parameters of Differential Signals" to achieve aforementioned impedance value. The trace length of the USB differential pair should be the same. You may want to consult with PCB layout engineer to obtain the exact parameters.

- The plane under the USB differential pair must be continuous. VSSAUSB is the best ground plane which should be placed under USB signals.

#### Power Trace Layout

PCB with dedicated power plane is recommended. If the PCB does not have a dedicated power plane (for example, a two layers PCB), then the power traces that connect the

power pin of USB connector to power regulator or directly to HDD, should be made as wide as possible. We suggest that the power trace width must be no less than 40mil.

- Follow the same rules to route the power traces output from power regulators.

- Place large capacitance capacitors at power pin of USB connector and at power input pin of power regulators. Electrolytic type capacitors are recommended.

- A USB mass storage device may consume more current than a single USB port can provide. Y-cable is recommended for this case. Make sure the USB cable is of good quality and could sustain the required amount current.

#### PCB Parameters of Differential Signals

(Assume 1oz cooper density)

| Туре                  | Material (dielectric<br>Constant) | PCB thickness | Dielectric<br>thickness | Trace width               | Trace spacing             |

|-----------------------|-----------------------------------|---------------|-------------------------|---------------------------|---------------------------|

| 2-layer <sup>6*</sup> | FR4 (4.2)                         | 1.6 mm        | 57 mil                  |                           | SATA : 5mil<br>USB : 5mil |

| 4-layer               | FR4 (4.2)                         | 1.6 mm        | 4.3 mil                 | SATA : 5mil<br>USB : 6mil | SATA :10mil<br>USB : 8mil |

<sup>&</sup>lt;sup>6</sup> The layout engineer MUST follow this note precisely for a 2-layer PCB architecture is not a standard micro strip transmission line structure. There is a definite requirement to the spacing between the differential trace and the nearby cooper plane of the same layer. For PCB parameters specified above, this defined spacing is 8mil for SATA and is 9mil for USB.

## **Electrical Characteristics**

This section contains electrical specifications for the *X*-*Wall FX*. Please note, however, stressing conditions beyond the "Absolute Maximum Ratings" may cause permanent damage to the *X*-*Wall FX* device. Operating beyond the "operating conditions" is not recommended and extended exposure beyond "operating conditions" may adversely affect life and reliability of the *X*-*Wall FX* device.

#### Absolute Maximum Ratings

| Symbol   | Parameter                   | Va   | Value |    |  |

|----------|-----------------------------|------|-------|----|--|

|          |                             | Min  | Max   |    |  |

| Ts       | Storage Temperature         | -55  | +125  | °C |  |

| Та       | Operating Temperature       | -45  | 90    | °C |  |

| VDD33    | 3.3V Digital Supply Voltage | -0.5 | 3.6   | V  |  |

| AVDD33   | 3.3V Analog Supply Voltage  | -0.5 | 3.6   | V  |  |

| VDD18    | 1.8V Digital Supply Voltage | -0.5 | 1.93  | V  |  |

| AVDD18   | 1.8V Analog Supply Voltage  | -0.5 | 1.93  | V  |  |

| VIN_IO33 | Input Signal Voltage        | -0.5 | 5     | V  |  |

|          | (Apply to 3.3V I/O pins)    |      |       |    |  |

| VO_IO33  | Output Signal Voltage       | -0.5 | VDD33 | V  |  |

|          | (Apply to 3.3V I/O pins)    |      |       |    |  |

## **DC Characteristics**

Operating Conditions: VDD33=AVDD33=3.3V (±9.09%),

#### VDD18=AVDD18=1.8V (±7.22%), GND=0V

| Symbol | Parameter                              | Va   | Value |    |

|--------|----------------------------------------|------|-------|----|

|        |                                        | Min  | Max   |    |

| VDD33  | 3.3V Digital Supply Voltage            | 3.0  | 3.6   | V  |

| AVDD33 | 3.3V Analog Supply Voltage             | 3.0  | 3.6   | V  |

| VDD18  | 1.8V Digital Supply Voltage            | 1.67 | 1.93  | v  |

| AVDD18 | 1.8V Analog Supply Voltage             | 1.67 | 1.93  | V  |

| IVDD33 | 3.3V Supply current (IVDD33 + IAVDD33) | 9    | 63    | mA |

| IVDD18 | 1.8V Supply current (IVDD18 + IAVDD18) | 53   | 212   | mA |

## X-Wall FX Configuration Management

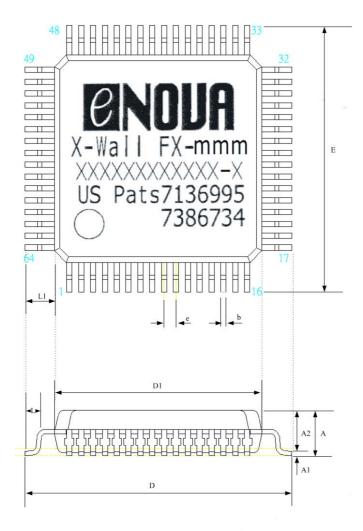

## Hardware Packaging

64-pin LQFP (Low-profile Quad Flat Package) provides low profile with 1.4mm body thickness, suitable for space concerned applications. Package size 7x7mm and lead-counts

64 are offered for portable, lightweight and low profile applications. All Enova X-Wall FX chips comply with RoHS and Leaf-free specification.

## Features

- 7mm x 7mm body size with 64 lead counts

- Copper lead frame

- ◆ Refer to JEDEC MA026(ISSUE D)/BBD

#### **Firmware Release**

Hard coded version 1.2.0 released for ROM integration within a silicon.

#### Hardware version control, outline, and dimension

| Symbol | Dimension [mm] |      |      |  |

|--------|----------------|------|------|--|

| Symbol | MIN            | NOM  | MAX  |  |

| е      | 0.4 BSC        |      |      |  |

| b      | 0.13           | 0.18 | 0.23 |  |

| D1     | 6.90           | 7.00 | 7.10 |  |

| D, E   | 8.90           | 9.00 | 9.10 |  |

| А      |                |      | 1.60 |  |

| A1     | 0.05           |      | 0.15 |  |

| A2     | 1.35           | 1.40 | 1.45 |  |

| L1     | 1.00 (REF)     |      |      |  |

| L      | 0.45           | 0.60 | 0.75 |  |

X-Wall FX top marking

Enova – Trademark

# **X-Wall FX-mmm**, product SKU where mmm represents 3 to 4 digits as follows:

- 256, AES ECB 256-bit

- 256C, AES CBC 256-bit

- 192, AES ECB 192-bit

- 192C, AES CBC 192-bit

- 128, AES ECB 128-bit

- 128C, AES CBC 128-bit

## XXXXXXXXXXXX-S

| 8 Lot No. | 4 date code | 2 version control|8 digits for wafer lot number;

4 digits yyww (yy represents year and ww represents week) for manufacturing date code;

2 digits –S for version control where S represents serial mixed signal design;

US Patent No.: granted US patents listing.